# TTSV02622 STS-24 Backplane Transceiver

#### **Features**

- Allows wide range of applications for SONET network termination application as well as generic data moving for high-speed backplane data transfer.

- Clock/data recovery (CDR) function for high-speed serial backplane data transfer.

- CDR function uses Agere Systems Inc. proven 622 Mbits/s serial interface core.

- Two-channel CDR function provides 622 Mbits/s serial interface per channel for a total chip bandwidth of 1.24 Gbits/s (full duplex).

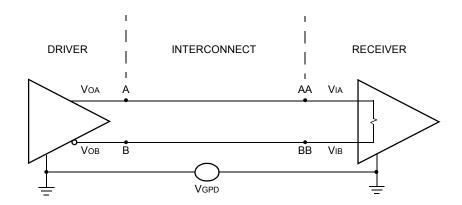

- Low-voltage differential signaling (LVDS) I/Os for CDR and reference clock signals.

- 8:1 data multiplexing/demultiplexing (MUX/ deMUX) for 77.76 MHz byte-wide data processing.

- CDR meets B jitter tolerance specification of ITU-T recommendation G.958.

- Powerdown option of CDR receiver on a perchannel basis.

- Pseudo-SONET protocol including A1/A2 framing.

- SONET scrambling and descrambling for required ones density (optional).

- Selected transport overhead (TOH) bytes insertion and detection for interdevice communication via the TOH serial link.

- Streamlined pointer processor (pointer mover) for 8 kHz frame alignment.

- FIFOs for alignment of incoming data to reference clock.

- FIFOs optionally align incoming data across all two channels for synchronous transport signal STS-24 operation (in dual STS-12 format).

- Independent data stream enables in pseudo-SONET processor.

- Supports STS-12/STS-24 redundancy by either software or hardware control for protection switching applications.

- Low-power 3.3 V supply.

- -40 °C to +125 °C industrial temperature range.

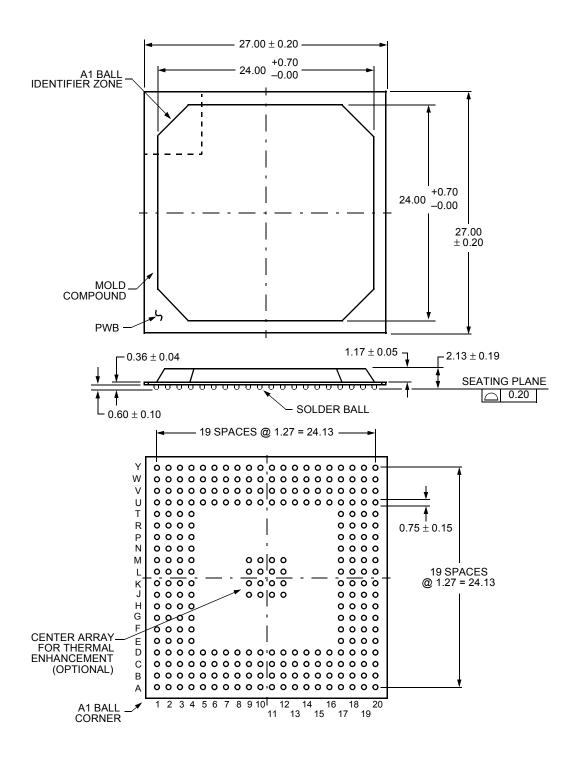

- 272-pin ball grid array (PBGA) package.

# Description

The TTSV02622 can support a 1.24 Gbits/s interface for backplane connections. The 1.24 Gbits/s interface is implemented as dual 622 Mbits/s LVDS links. The HSI macrocell is used for clock/data recovery (CDR) and MUX/deMUX between 77.76 MHz bytewide internal data buses and the 622 Mbits/s external serial links.

Each 622 Mbits/s serial link uses a pseudo-SONET protocol. SONET A1/A2 framing is used on the link for locating the 8 kHz frame location. The link is also scrambled using the standard SONET scrambler definition to ensure proper transitions on the link for improved CDR performance. Selectable transport overhead (TOH) bytes are insertable in the transmit direction. All bytes can be transparently passed through the device, or all bytes can be inserted via the TOH serial link. In addition, certain microprocessor unit (MPU) selectable bytes can be passed through transparently while in insert mode.

Elastic buffers (FIFOs) are used to align each incoming STS-12 link to the core 77.76 MHz clock and 8 kHz frame. These FIFOs will absorb delay variations between 622 Mbits/s links due to timing skews between cards and along backplane traces. For greater variations, a streamlined pointer processor (pointer mover) within the device will align the 8 kHz frames regardless of their incoming frame position.

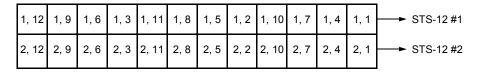

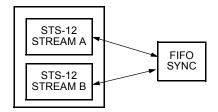

The TTSV02622 supports dual STS-12 mode of operation on the input/output ports. STS-24 is also supported, but it must be received in the dual STS-12 format. When operating in dual STS-12 mode, each of the independent byte streams carries an entire STS-12 within it. Figure 1 on page 2 reveals the byte ordering of the individual STS-12 streams.

# **Description** (continued)

STS-24 IN DUAL STS-12 FORMAT

**DUAL STS-12**

Figure 1. Byte Ordering on Input/Output Interface in STS-12 Mode

# **Table of Contents**

| Contents                                        | Page |

|-------------------------------------------------|------|

| Features                                        | 1    |

| Description                                     |      |

| Pin Information                                 |      |

| Synchronization                                 | 17   |

| HSI Block Interface                             |      |

| Line Interface                                  |      |

| Architecture                                    | 17   |

| Powerdown Mode                                  |      |

| Supervisory Features                            |      |

| Test Features                                   |      |

| Transmit Direction (Line to Backplane)          |      |

| Transport Overhead Serial Link                  |      |

| A1/A2 Frame Insert and Corruption               | 23   |

| B1 Calculation and Insertion                    |      |

| Stream Disable                                  |      |

| Scrambler                                       |      |

| Receiver Block                                  | 24   |

| Framer Subblock (Backplane to Line)             | 24   |

| B1 Calculate and Descramble (Backplane to Line) |      |

| Internal Parity Generation                      |      |

| FIFO Subblock (Backplane to Line)               |      |

| Pointer Mover Subblock (Backplane to Line)      |      |

| Miscellaneous Functions                         |      |

| K1/K2, A1/A2 Handling                           | 31   |

| SPE C1J1 Outputs                                |      |

| Registers                                       |      |

| Definition of Register Types                    |      |

| Register Map                                    |      |

| Register Descriptions                           |      |

| Absolute Maximum Ratings                        |      |

| Handling Precautions                            |      |

| Recommended Operating Conditions                |      |

| Thermal Characteristics                         |      |

| Power Consumption (Advance)                     | 49   |

| Electrical Characteristics                      |      |

| Propagation Delay Specifications                | 49   |

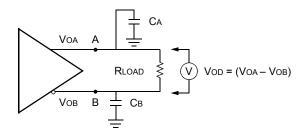

| LVDS I/O                                        | 50   |

| LVDS Receiver Buffer Capabilities               | 52   |

| Clock and Data Recovery (CDR)                   |      |

| Input Data                                      | 54   |

| Jitter Tolerance                                | 54   |

| Generated Output Jitter                         | 54   |

| PLL                                             |      |

| Input Reference Clock                           |      |

| Timing Characteristics                          |      |

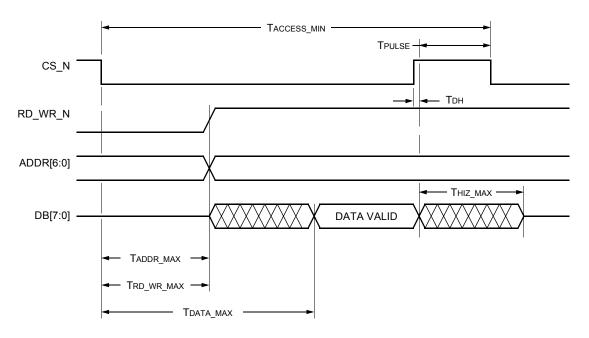

| CPU Interface Timing                            |      |

| Outline Diagram                                 |      |

| 272-Pin PBGA                                    |      |

| Ordering Information                            |      |

# **List of Figures**

| Contents                                                               | Page |

|------------------------------------------------------------------------|------|

| Figure 1. Byte Ordering on Input/Output Interface in STS-12 Mode       | 2    |

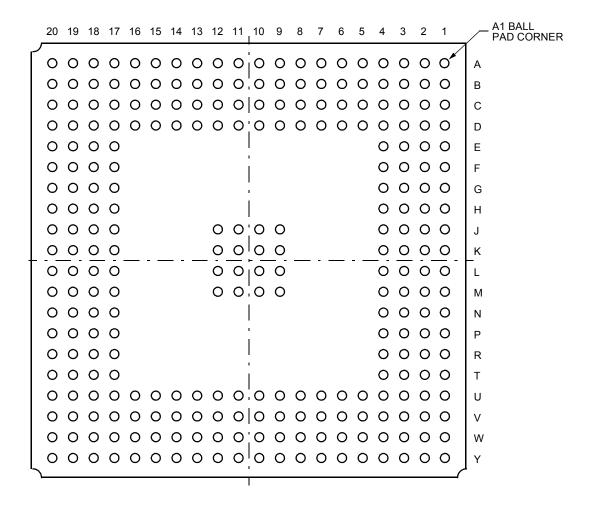

| Figure 2. Pin Diagram of 272-Pin PBGA (Bottom View)                    | 6    |

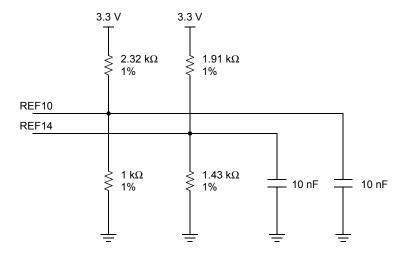

| Figure 3. Suggested Schematic for 1.0 V and 1.4 V Reference Voltages   | 16   |

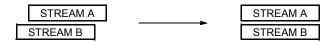

| Figure 4. Alignment of Two STS-12 Streams                              | 17   |

| Figure 5. Interior View of TTSV02622                                   | 18   |

| Figure 6. Interconnect of Streams for FIFO Alignment                   | 19   |

| Figure 7. Transmitter Block                                            | 22   |

| Figure 8. Receiver Block                                               | 24   |

| Figure 9. Framer State Machine                                         | 26   |

| Figure 10. Pointer Mover State Machine                                 | 30   |

| Figure 11. LVDS Driver and Receiver and Associated Internal Components | 51   |

| Figure 12. LVDS Driver and Receiver                                    |      |

| Figure 13. LVDS Driver                                                 |      |

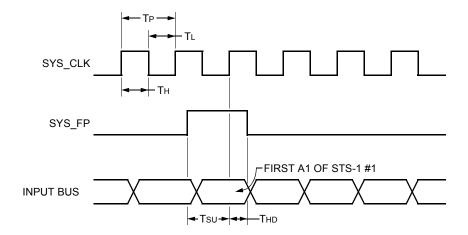

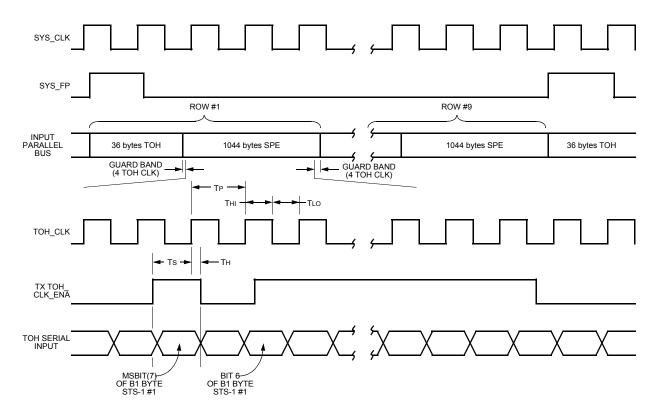

| Figure 14. Input Parallel Port Timing                                  | 55   |

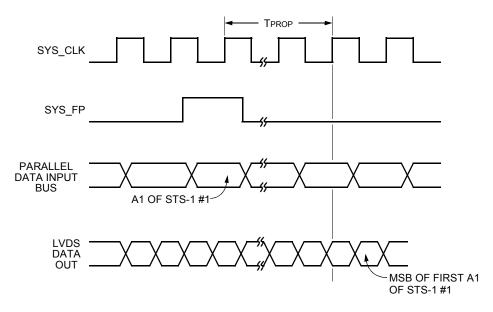

| Figure 15. Transmitter Transport Delay                                 | 56   |

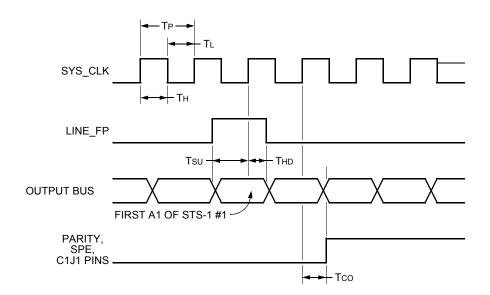

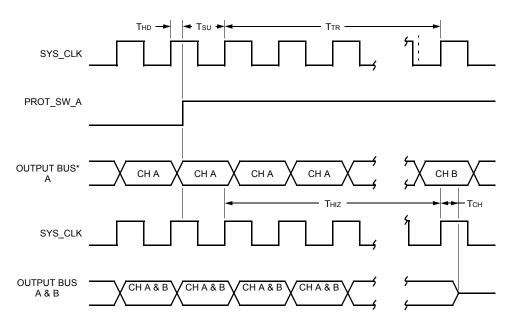

| Figure 16. Output Parallel Port Timing                                 |      |

| Figure 17. Protection Switch Timing                                    |      |

| Figure 18. Input Serial Port Timing                                    |      |

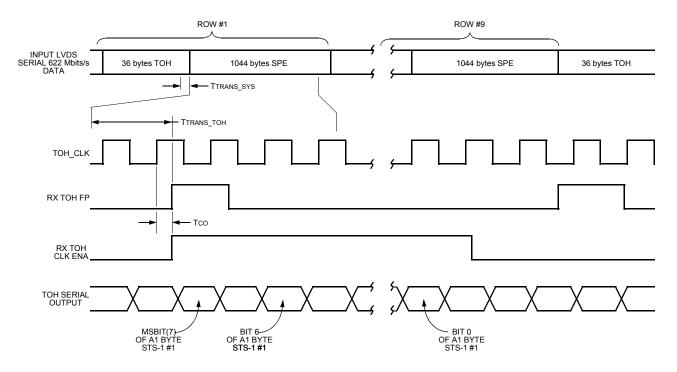

| Figure 19. Output Serial Port Timing                                   |      |

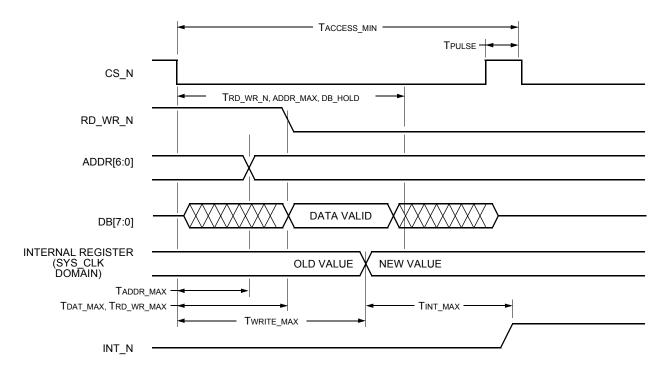

| Figure 20. Write Transaction                                           |      |

| Figure 21 Read Transaction                                             | 62   |

# **List of Tables**

| Contents                                                      | Page |

|---------------------------------------------------------------|------|

| Table 1. Pin Assignments for 272-Pin PBGA by Pin Number Order | 7    |

| Table 2. Pin Assignments for 272-Pin PBGA by Signal Name      |      |

| Table 3. Pin Descriptions                                     | 12   |

| Table 4. Valid Starting Positions for a STS-MC                | 29   |

| Table 5. SPE and C1J1 Functionality                           | 31   |

| Table 6. Register Map                                         | 33   |

| Table 7. Register Description                                 | 36   |

| Table 8. Absolute Maximum Ratings                             | 48   |

| Table 9. Handling Precautions                                 | 48   |

| Table 10. Recommended Operating Conditions                    |      |

| Table 11. Thermal Resistance—Junction to Ambient              |      |

| Table 12. Power Consumption (Advance)                         |      |

| Table 13. LVTTL Electrical Characteristics                    |      |

| Table 14. LVDS Receiver dc Data*                              |      |

| Table 15. LVDS Receiver ac Data*                              |      |

| Table 16. LVDS Driver dc Data*                                |      |

| Table 17. LVDS Driver ac Data*                                |      |

| Table 18. LVDS Driver Reference Data                          |      |

| Table 19. Jitter Tolerance                                    |      |

| Table 20. Input Parallel Port Timing Requirements             |      |

| Table 21. Transmitter Transport Delay Timing Requirements     |      |

| Table 22. Output Parallel Port Timing Requirements            |      |

| Table 23. Protection Switch Timing Requirements               |      |

| Table 24. Input Serial Port Timing Requirements               |      |

| Table 25. Output Serial Port Timing Requirements              |      |

| Table 26. Write Transaction Timing Requirements               |      |

| Table 27. Read Transaction Timing Requirements                | 62   |

## **Pin Information**

Figure 2. Pin Diagram of 272-Pin PBGA (Bottom View)

Table 1. Pin Assignments for 272-Pin PBGA by Pin Number Order

| Pin | Signal Name   | Pin | Signal Name   | Pin | Signal Name | Pin | Signal Name |

|-----|---------------|-----|---------------|-----|-------------|-----|-------------|

| A1  | Vss           | B1  | TDO           | C1  | NC          | D1  | NC          |

| A2  | TCK           | B2  | TRSTN         | C2  | NC          | D2  | NC          |

| A3  | TDI           | В3  | TSTMD         | C3  | LVDS_EN     | D3  | NC          |

| A4  | TMS           | B4  | SCANEN        | C4  | NC          | D4  | Vss         |

| A5  | DXP           | B5  | NC            | C5  | NC          | D5  | NC          |

| A6  | NC            | В6  | DXN           | C6  | NC          | D6  | VDD         |

| A7  | PROT_SWITCH_A | В7  | PROT_SWITCH_C | C7  | NC          | D7  | NC          |

| A8  | TOH_INA       | B8  | TOH_INB       | C8  | TX_TOH_CKEN | D8  | Vss         |

| A9  | NC            | В9  | NC            | C9  | TOH_CLK     | D9  | NC          |

| A10 | NC            | B10 | NC            | C10 | NC          | D10 | NC          |

| A11 | TOH_OUTA      | B11 | TOH_OUTB      | C11 | RX_TOH_CKEN | D11 | VDD         |

| A12 | NC            | B12 | NC            | C12 | RX_TOH_FP   | D12 | NC          |

| A13 | NC            | B13 | NC            | C13 | NC          | D13 | Vss         |

| A14 | NC            | B14 | NC            | C14 | NC          | D14 | NC          |

| A15 | DOUTA7        | B15 | DOUTA6        | C15 | DOUTA5      | D15 | Vdd         |

| A16 | DOUTA4        | B16 | DOUTA3        | C16 | DOUTA2      | D16 | DOUTA1      |

| A17 | DOUTA0        | B17 | DOUTA_PAR     | C17 | DOUTA_SPE   | D17 | Vss         |

| A18 | DOUTA_C1J1    | B18 | DOUTB5        | C18 | DOUTB2      | D18 | DOUTB_PAR   |

| A19 | DOUTB7        | B19 | DOUTB4        | C19 | DOUTB1      | D19 | DOUTB_SPE   |

| A20 | DOUTB6        | B20 | DOUTB3        | C20 | DOUTB0      | D20 | DOUTB_C1J1  |

Note: NC refers to no connect. Do not connect pins so designated.

Table 1. Pin Assignments for 272-Pin PBGA by Pin Number Order (continued)

| Pin | Signal Name |

|-----|-------------|-----|-------------|-----|-------------|-----|-------------|

| E1  | STS_INA_P   | H17 | Vss         | L1  | STS_OUTB_P  | N17 | Vss         |

| E2  | STS_INA_N   | H18 | NC          | L2  | STS_OUTB_N  | N18 | DINA7       |

| E3  | CTAP_REFA   | H19 | NC          | L3  | NC          | N19 | DINA6       |

| E4  | NC          | H20 | NC          | L4  | NC          | N20 | DINA5       |

| E17 | NC          | J1  | STS_OUTA_P  | L9  | Vss         | P1  | NC          |

| E18 | NC          | J2  | STS_OUTA_N  | L10 | Vss         | P2  | NC          |

| E19 | NC          | J3  | NC          | L11 | Vss         | P3  | NC          |

| E20 | NC          | J4  | NC          | L12 | Vss         | P4  | NC          |

| F1  | STS_INB_P   | J9  | Vss         | L17 | Vdd         | P17 | DINA4       |

| F2  | STS_INB_N   | J10 | Vss         | L18 | NC          | P18 | DINA3       |

| F3  | CTAP_REFB   | J11 | Vss         | L19 | NC          | P19 | DINA2       |

| F4  | Vdd         | J12 | Vss         | L20 | NC          | P20 | DINA1       |

| F17 | VDD         | J17 | NC          | M1  | REF10       | R1  | NC          |

| F18 | NC          | J18 | NC          | M2  | REF14       | R2  | NC          |

| F19 | NC          | J19 | NC          | M3  | LVDS_RESH   | R3  | NC          |

| F20 | NC          | J20 | NC          | M4  | LVDS_RESL   | R4  | Vdd         |

| G1  | NC          | K1  | PLL REF     | M9  | Vss         | R17 | VDD         |

| G2  | NC          | K2  | PLL_VDDA    | M10 | Vss         | R18 | DINB7       |

| G3  | NC          | K3  | PLL_VSSA    | M11 | Vss         | R19 | DINA0       |

| G4  | NC          | K4  | Vdd         | M12 | Vss         | R20 | DINA_PAR    |

| G17 | NC          | K9  | Vss         | M17 | SYS_CLK     | T1  | TSTMODE     |

| G18 | NC          | K10 | Vss         | M18 | SYS_FP      | T2  | BYPASS      |

| G19 | NC          | K11 | Vss         | M19 | LINE_FP     | T3  | RESETRN     |

| G20 | NC          | K12 | Vss         | M20 | NC          | T4  | RESETTN     |

| H1  | NC          | K17 | NC          | N1  | NC          | T17 | DINB6       |

| H2  | NC          | K18 | NC          | N2  | NC          | T18 | DINB5       |

| Н3  | NC          | K19 | NC          | N3  | NC          | T19 | DINB4       |

| H4  | Vss         | K20 | NC          | N4  | Vss         | T20 | DINB3       |

Note: NC refers to no connect. Do not connect pins so designated.

Table 1. Pin Assignments for 272-Pin PBGA by Pin Number Order (continued)

| Pin | Signal Name |

|-----|-------------|-----|-------------|-----|-------------|-----|-------------|

| U1  | TSTCLK      | V1  | MRESET      | W1  | EXDNUP      | Y1  | NC          |

| U2  | TSTSHFTLD   | V2  | ECSEL       | W2  | TSTPHASE    | Y2  | NC          |

| U3  | ETOGGLE     | V3  | LOOPBKEN    | W3  | TSTMUX8S    | Y3  | TSTMUX7S    |

| U4  | Vss         | V4  | TSTMUX6S    | W4  | TSTMUX5S    | Y4  | TSTMUX4S    |

| U5  | TSTMUX3S    | V5  | TSTMUX2S    | W5  | TSTMUX1S    | Y5  | TSTMUX0S    |

| U6  | VDD         | V6  | NC          | W6  | NC          | Y6  | NC          |

| U7  | CPU_ADDR6   | V7  | CPU_ADDR5   | W7  | CPU_ADDR4   | Y7  | CPU_ADDR3   |

| U8  | Vss         | V8  | CPU_ADDR2   | W8  | CPU_ADDR1   | Y8  | CPU_ADDR0   |

| U9  | CS_N        | V9  | RD_WRN      | W9  | RST_N       | Y9  | HIZ_N       |

| U10 | VDD         | V10 | INT_N       | W10 | NC          | Y10 | NC          |

| U11 | CPU_DATA7   | V11 | CPU_DATA6   | W11 | CPU_DATA5   | Y11 | CPU_DATA4   |

| U12 | CPU_DATA3   | V12 | CPU_DATA2   | W12 | CPU_DATA1   | Y12 | CPU_DATA0   |

| U13 | Vss         | V13 | NC          | W13 | NC          | Y13 | NC          |

| U14 | NC          | V14 | NC          | W14 | NC          | Y14 | NC          |

| U15 | VDD         | V15 | NC          | W15 | NC          | Y15 | NC          |

| U16 | DIND4       | V16 | NC          | W16 | NC          | Y16 | NC          |

| U17 | Vss         | V17 | NC          | W17 | NC          | Y17 | NC          |

| U18 | DINB2       | V18 | NC          | W18 | NC          | Y18 | NC          |

| U19 | DINB1       | V19 | NC          | W19 | NC          | Y19 | NC          |

| U20 | DINB0       | V20 | DINB_PAR    | W20 | NC          | Y20 | NC          |

Note: NC refers to no connect. Do not connect pins so designated.

Table 2. Pin Assignments for 272-Pin PBGA by Signal Name

| Signal Name | Pin |

|-------------|-----|-------------|-----|-------------|-----|-------------|-----|

| BYPASS      | T2  | DINB4       | T19 | LINE_FP     | M19 | NC          | D12 |

| CPU_ADDR0   | Y8  | DINB5       | T18 | LOOPBKEN    | V3  | NC          | D14 |

| CPU_ADDR1   | W8  | DINB6       | T17 | LVDS_EN     | C3  | NC          | E4  |

| CPU_ADDR2   | V8  | DINB7       | R18 | LVDS_RESH   | М3  | NC          | E17 |

| CPU_ADDR3   | Y7  | DIND4       | U16 | LVDS_RESL   | M4  | NC          | E18 |

| CPU_ADDR4   | W7  | DOUTA_C1J1  | A18 | MRESET      | V1  | NC          | E19 |

| CPU_ADDR5   | V7  | DOUTA_PAR   | B17 | NC          | A6  | NC          | E20 |

| CPU_ADDR6   | U7  | DOUTA_SPE   | C17 | NC          | A9  | NC          | F18 |

| CPU_DATA0   | Y12 | DOUTA0      | A17 | NC          | A10 | NC          | F19 |

| CPU_DATA1   | W12 | DOUTA1      | D16 | NC          | A12 | NC          | F20 |

| CPU_DATA2   | V12 | DOUTA2      | C16 | NC          | A13 | NC          | G1  |

| CPU_DATA3   | U12 | DOUTA3      | B16 | NC          | A14 | NC          | G2  |

| CPU_DATA4   | Y11 | DOUTA4      | A16 | NC          | B5  | NC          | G3  |

| CPU_DATA5   | W11 | DOUTA5      | C15 | NC          | В9  | NC          | G4  |

| CPU_DATA6   | V11 | DOUTA6      | B15 | NC          | B10 | NC          | G17 |

| CPU_DATA7   | U11 | DOUTA7      | A15 | NC          | B12 | NC          | G18 |

| CS_N        | U9  | DOUTB_C1J1  | D20 | NC          | B13 | NC          | G19 |

| CTAP_REFA   | E3  | DOUTB_PAR   | D18 | NC          | B14 | NC          | G20 |

| CTAP_REFB   | F3  | DOUTB_SPE   | D19 | NC          | C1  | NC          | H1  |

| DINA_PAR    | R20 | DOUTB0      | C20 | NC          | C2  | NC          | H2  |

| DINA0       | R19 | DOUTB1      | C19 | NC          | C4  | NC          | H3  |

| DINA1       | P20 | DOUTB2      | C18 | NC          | C5  | NC          | H18 |

| DINA2       | P19 | DOUTB3      | B20 | NC          | C6  | NC          | H19 |

| DINA3       | P18 | DOUTB4      | B19 | NC          | C7  | NC          | H20 |

| DINA4       | P17 | DOUTB5      | B18 | NC          | C10 | NC          | J3  |

| DINA5       | N20 | DOUTB6      | A20 | NC          | C13 | NC          | J4  |

| DINA6       | N19 | DOUTB7      | A19 | NC          | C14 | NC          | J17 |

| DINA7       | N18 | DXN         | В6  | NC          | D1  | NC          | J18 |

| DINB_PAR    | V20 | DXP         | A5  | NC          | D2  | NC          | J19 |

| DINB0       | U20 | ECSEL       | V2  | NC          | D3  | NC          | J20 |

| DINB1       | U19 | ETOGGLE     | U3  | NC          | D5  | NC          | K17 |

| DINB2       | U18 | EXDNUP      | W1  | NC          | D7  | NC          | K18 |

| DINB3       | T20 | HIZ_N       | Y9  | NC          | D9  | NC          | K19 |

| DINB3       | T20 | INT_N       | V10 | NC          | D10 | NC          | K20 |

Note: NC refers to no connect. Do not connect pins so designated.

Table 2. Pin Assignments for 272-Pin PBGA by Signal Name (continued)

| Signal Name | Pin | Signal Name   | Pin | Signal Name | Pin | Signal Name | Pin |

|-------------|-----|---------------|-----|-------------|-----|-------------|-----|

| NC          | L3  | NC            | W20 | STS_OUTB_P  | L1  | VDD         | L17 |

| NC          | L4  | NC            | Y1  | SYS_CLK     | M17 | VDD         | R4  |

| NC          | L18 | NC            | Y2  | SYS_FP      | M18 | VDD         | R17 |

| NC          | L19 | NC            | Y6  | TCK         | A2  | VDD         | U6  |

| NC          | L20 | NC            | Y10 | TDI         | A3  | VDD         | U10 |

| NC          | M20 | NC            | Y13 | TDO         | B1  | VDD         | U15 |

| NC          | N1  | NC            | Y14 | TMS         | A4  | Vss         | A1  |

| NC          | N2  | NC            | Y15 | TOH_CLK     | C9  | Vss         | D4  |

| NC          | N3  | NC            | Y16 | TOH_INA     | A8  | Vss         | D8  |

| NC          | P1  | NC            | Y17 | TOH_INB     | B8  | Vss         | D13 |

| NC          | P2  | NC            | Y18 | TOH_OUTA    | A11 | Vss         | D17 |

| NC          | P3  | NC            | Y19 | TOH_OUTB    | B11 | Vss         | H4  |

| NC          | P4  | NC            | Y20 | TRSTN       | B2  | Vss         | H17 |

| NC          | R1  | PLL REF       | K1  | TSTCLK      | U1  | Vss         | J9  |

| NC          | R2  | PLL_VDDA      | K2  | TSTMD       | В3  | Vss         | J10 |

| NC          | R3  | PLL_VSSA      | K3  | TSTMODE     | T1  | Vss         | J11 |

| NC          | U14 | PROT_SWITCH_A | Α7  | TSTMUX0S    | Y5  | Vss         | J12 |

| NC          | V6  | PROT_SWITCH_C | В7  | TSTMUX1S    | W5  | Vss         | K9  |

| NC          | V13 | RD_WRN        | V9  | TSTMUX2S    | V5  | Vss         | K10 |

| NC          | V14 | REF10         | M1  | TSTMUX3S    | U5  | Vss         | K11 |

| NC          | V15 | REF14         | M2  | TSTMUX4S    | Y4  | Vss         | K12 |

| NC          | V16 | RESETRN       | T3  | TSTMUX5S    | W4  | Vss         | L9  |

| NC          | V17 | RESETTN       | T4  | TSTMUX6S    | V4  | Vss         | L10 |

| NC          | V18 | RST_N         | W9  | TSTMUX7S    | Y3  | Vss         | L11 |

| NC          | V19 | RX_TOH_CKEN   | C11 | TSTMUX8S    | W3  | Vss         | L12 |

| NC          | W6  | RX_TOH_FP     | C12 | TSTPHASE    | W2  | Vss         | M9  |

| NC          | W10 | SCANEN        | В4  | TSTSHFTLD   | U2  | Vss         | M10 |

| NC          | W13 | STS_INA_N     | E2  | TX_TOH_CKEN | C8  | Vss         | M11 |

| NC          | W14 | STS_INA_P     | E1  | VDD         | D6  | Vss         | M12 |

| NC          | W15 | STS_INB_N     | F2  | VDD         | D11 | Vss         | N4  |

| NC          | W16 | STS_INB_P     | F1  | VDD         | D15 | Vss         | N17 |

| NC          | W17 | STS_OUTA_N    | J2  | VDD         | F4  | Vss         | U4  |

| NC          | W18 | STS_OUTA_P    | J1  | VDD         | F17 | Vss         | U8  |

| NC          | W19 | STS_OUTB_N    | L2  | VDD         | K4  | Vss         | U13 |

| _           |     | _             |     | _           |     | Vss         | U17 |

Note: NC refers to no connect. Do not connect pins so designated.

**Table 3. Pin Descriptions**

| Pin                                          | Symbol      | Туре | I/O                    | Description                                          |

|----------------------------------------------|-------------|------|------------------------|------------------------------------------------------|

| N18, N19, N20,<br>P17, P18, P19,<br>P20, R19 | DINA[7:0]   | TTL  | I/<br>Pull-up          | Input parallel bus of transmitter #1.                |

| R20                                          | DINA_PAR    | TTL  | l/<br>Pull-up          | Parity for input bus of transmitter #1.              |

| R18, T17, T18,<br>T19, T20, U18,<br>U19, U20 | DINB[7:0]   | TTL  | l/<br>Pull-up          | Input parallel bus of transmitter #2.                |

| V20                                          | DINB_PAR    | TTL  | l/<br>Pull-up          | Parity for input bus of transmitter #2.              |

| A15, B15, C15,<br>A16, B16, C16,<br>D16, A17 | DOUTA[7:0]  | TTL  | O/<br>HI-Z/<br>Pull-up | Output parallel bus of receiver #1.                  |

| B17                                          | DOUTA_PAR   | TTL  | O/<br>HI-Z/<br>Pull-up | Parity for output parallel bus of receiver #1.       |

| C17                                          | DOUTA_SPE   | TTL  | O/<br>HI-Z/<br>Pull-up | SPE signal for output parallel bus of receiver #1.   |

| A18                                          | DOUTA_C1J1  | TTL  | O/<br>HI-Z/<br>Pull-up | C1J1 signal for output parallel bus of receiver #1.  |

| A19, A20, B18,<br>B19, B20, C18,<br>C19, C20 | DOUTB[7:0]  | TTL  | O/<br>HI-Z/<br>Pull-up | Output parallel bus of receiver #2.                  |

| D18                                          | DOUTB_PAR   | TTL  | O/<br>HI-Z/<br>Pull-up | Parity for output parallel bus of receiver #2.       |

| D19                                          | DOUTB_SPE   | TTL  | O/<br>HI-Z/<br>Pull-up | SPE signal for output parallel bus of receiver #2.   |

| D20                                          | DOUTB_C1J1  | TTL  | O/<br>HI-Z/<br>Pull-up | C1J1 signal for output parallel bus of receiver #2.  |

| C9                                           | TOH_CLK     | TTL  | l/<br>Pull-up          | Tx and Rx TOH serial links clock (25 MHz—77.76 MHz). |

| A8                                           | TOH_INA     | TTL  | l/<br>Pull-up          | TOH serial link input for transmitter #1.            |

| B8                                           | TOH_INB     | TTL  | I/<br>Pull-up          | TOH serial link input for transmitter #2.            |

| C8                                           | TX_TOH_CKEN | TTL  | I/<br>Pull-up          | Tx TOH serial link clock enable.                     |

| A11                                          | TOH_OUTA    | TTL  | O/<br>HI-Z/<br>Pull-up | TOH serial link output for receiver #1.              |

**Table 3. Pin Descriptions** (continued)

| Pin                                          | Symbol        | Туре | I/O                         | Description                                         |

|----------------------------------------------|---------------|------|-----------------------------|-----------------------------------------------------|

| B11                                          | TOH_OUTB      | TTL  | O/<br>HI-Z/<br>Pull-up      | TOH serial link output for receiver #2.             |

| C11                                          | RX_TOH_CKEN   | TTL  | O/<br>HI-Z/<br>Pull-up      | Rx TOH serial link clock enable.                    |

| C12                                          | RX_TOH_FP     | TTL  | O/<br>HI-Z/<br>Pull-up      | Rx TOH serial link frame pulse.                     |

| E1                                           | STS_INA_P     | LVDS | ı                           | LVDS input receiver #1.                             |

| E2                                           | STS_INA_N     | LVDS |                             | LVDS input receiver #1.                             |

| F1                                           | STS_INB_P     | LVDS | I                           | LVDS input receiver #2.                             |

| F2                                           | STS_INB_N     | LVDS | I                           | LVDS input receiver #2.                             |

| J1                                           | STS_OUTA_P    | LVDS | 0                           | LVDS output transmitter #1.                         |

| J2                                           | STS_OUTA_N    | LVDS | 0                           | LVDS output transmitter #1.                         |

| L1                                           | STS_OUTB_P    | LVDS | 0                           | LVDS output transmitter #2.                         |

| L2                                           | STS OUTB N    | LVDS | 0                           | LVDS output transmitter #2.                         |

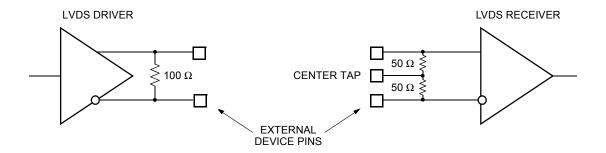

| E3                                           | CTAP_REFA     | _    |                             | LVDS input center tap (Rx #1) (use 0.01 µF to GND). |

| F3                                           | CTAP_REFB     | _    |                             | LVDS input center tap (Rx #2) (use 0.01 µF to GND). |

| U11, V11, W11,<br>Y11, U12, V12,<br>W12, Y12 | CPU_DATA[7:0] | TTL  | I/<br>O/<br>Pull-up         | Central processing unit (CPU) interface data bus.   |

| U7, V7, W7, Y7,<br>V8, W8, Y8                | CPU_ADDR[6:0] | TTL  | I/<br>Pull-up               | CPU interface address bus.                          |

| V9                                           | RD_WRN        | TTL  | I/Pull-Up                   | CPU interface read/write.                           |

| U9                                           | CS_N          | TTL  | I/<br>Pull-up<br>SCHMITT    | Chip select.                                        |

| M18                                          | SYS_FP        | TTL  | I/<br>Pull-up               | System frame pulse for transmitter section.         |

| M19                                          | LINE_FP       | TTL  | I/<br>Pull-up               | Line frame pulse for receiver section.              |

| M17                                          | SYS_CLK       | TTL  | I/<br>Pull-up               | System clock (77.76 MHz).                           |

| A7                                           | PROT_SW_A     | TTL  | I/<br>Pull-up               | Protection switching control signal.                |

| B7                                           | PROT_SW_C     | TTL  | l/<br>Pull-up               | Protection switching control signal.                |

| V10                                          | INT_N         | TTL  | O/<br>Open<br>Drain         | Interrupt output.                                   |

| W9                                           | RST_N         | TTL  | I/<br>Pull-down/<br>SCHMITT | Global reset.                                       |

Table 3. Pin Descriptions (continued)

| Pin | Symbol    | Туре | I/O                       | Description                                                                             |

|-----|-----------|------|---------------------------|-----------------------------------------------------------------------------------------|

| Y9  | HIZ_N     | TTL  | I/<br>Pull-up/<br>SCHMITT | Global 3-state control.                                                                 |

| K1  | PLL_REF   |      | _                         | Reference for PLL (10 $k\Omega$ to GND).                                                |

| M1  | REF10     | _    | I                         | 1.0 V reference for LVDS reference block. See Figure 3 on page 16.                      |

| M2  | REF14     | _    | I                         | 1.4 V reference for LVDS reference block. See Figure 3 on page 16.                      |

| M3  | LVDS_RESH | _    | _                         | Resistance high input (use 100 $\Omega$ to LVDS_RESL input).                            |

| M4  | LVDS_RESL | _    | _                         | Resistance low input (use 100 $\Omega$ to LVDS_RESH input).                             |

| A5  | DXP       | _    | _                         | Temperature-sensing diode (anode +).                                                    |

| B6  | DXN       | _    | _                         | Temperature-sensing diode (cathode –).                                                  |

| K2  | PLL_VDDA  | _    | _                         | PLL analog VDD (3.3 V).                                                                 |

| K3  | PLL_VSSA  | _    | _                         | PLL analog Vss (GND).                                                                   |

| A2  | TCLK      | TTL  | l/<br>Pull-up             | JTAG clock input.                                                                       |

| A3  | TDI       | TTL  | I/<br>Pull-up             | JTAG data input.                                                                        |

| A4  | TMS       | TTL  | I/<br>Pull-up             | JTAG mode select input.                                                                 |

| B1  | TDO       | TTL  | 0                         | JTAG data output.                                                                       |

| B2  | TRSTN     | TTL  | I/<br>Pull-up             | JTAG reset input.                                                                       |

| В3  | TSTMD     | TTL  | I/<br>Pull-up             | Scan test mode input.                                                                   |

| B4  | SCANEN    | TTL  | I/<br>Pull-Up             | Scan mode enable input.                                                                 |

| C3  | LVDS_EN   | _    | I/<br>Pull-up             | LVDS enable used during boundary scan (B-S).                                            |

| T1  | TSTMODE   | _    | I/<br>Pull-down           | Enables CDR test mode.                                                                  |

| T2  | BYPASS    | _    | l/<br>Pull-down           | Enables bypassing of the 622 MHz clock synthesis with TSTCLK.                           |

| U1  | TSTCLK    | _    | l/<br>Pull-down           | Test clock for emulation of 622 MHz clock during PLL bypass.                            |

| V1  | MRESET    | _    | l/<br>Pull-down           | Test mode reset.                                                                        |

| Т3  | RESETRN   | _    | l/<br>Pull-up             | Resets receiver clock division counter.                                                 |

| T4  | RESETTN   | _    | I/<br>Pull-up             | Resets transmitter clock division counter.                                              |

| U2  | TSTSHFTLD | _    | l/<br>Pull-down           | Enables the test mode control register for shifting-in selected tests by a serial port. |

**Table 3. Pin Descriptions** (continued)

| Pin                                  | Symbol       | Type | I/O       | Description                                          |

|--------------------------------------|--------------|------|-----------|------------------------------------------------------|

| V2                                   | ECSEL        | _    | 1/        | Enables external test control of 622 MHz clock phase |

|                                      |              |      | Pull-down | selection.                                           |

| W1                                   | EXDNUP       | _    | 1/        | Direction of phase change.                           |

|                                      |              |      | Pull-down |                                                      |

| U3                                   | ETOGGLE      | _    | 1/        | Moves 622.08 MHz clock selection on phase per        |

|                                      |              |      | Pull-down | positive pulse.                                      |

| V3                                   | LOOPBKEN     | _    | 1/        | Enables 622 Mbits/s loopback mode.                   |

|                                      |              |      | Pull-Down |                                                      |

| W2                                   | TSTPHASE     | _    | 1/        | Controls bypass of 16 PLL-generated phases with      |

|                                      |              |      | Pull-down | 16 low-speed phases.                                 |

| W3, Y3, V4, W4,                      | TSTMUX[8:0]S | _    | 0         | Test mode output port.                               |

| Y4, U5, V5, W5, Y5                   |              |      |           |                                                      |

| A1, D4, D8, D13,                     | Vss          | _    | _         | _                                                    |

| D17, H4, H17, N4,                    |              |      |           |                                                      |

| N17, U4, U8, U13, U17, J9, J10, J11, |              |      |           |                                                      |

| J12, K9, K10, K11,                   |              |      |           |                                                      |

| K12, L9, L10, L11,                   |              |      |           |                                                      |

| L12, M9, M10,                        |              |      |           |                                                      |

| M11, M12                             |              |      |           |                                                      |

| D6, D11, D15, F4,                    | Vdd          | _    | _         | _                                                    |

| F17, K4, L17, R4,                    |              |      |           |                                                      |

| R17, U6, U10, U15                    |              |      |           |                                                      |

Figure 3. Suggested Schematic for 1.0 V and 1.4 V Reference Voltages

# **Synchronization**

The incoming data from the high-speed interface (HSI) can be separated into two STS-12 channels per slice (A and B).

Example of TTSV02622 alignment.

Figure 4. Alignment of Two STS-12 Streams

There is also a provision to allow certain streams to be disabled (i.e., not producing interrupts or affecting synchronization). These streams can be enabled at a later time without disrupting other streams.

#### **HSI Block Interface**

The HSI block should provide two independent 77.76 MHz interfaces. Each interface will consist of a byte-wide data stream and its recovered clock. There is no requirement for bit alignment since SONET type framing will take place inside the TTSV02622 device.

## **Line Interface**

The line side will receive/transmit frame-aligned streams of STS-12 data. All frames transmitted to the line will be aligned to the line frame pulse, which will be provided to the TTSV02622. All frames received from the line will be aligned to the system frame pulse, which will be supplied to the TTSV02622.

#### **Architecture**

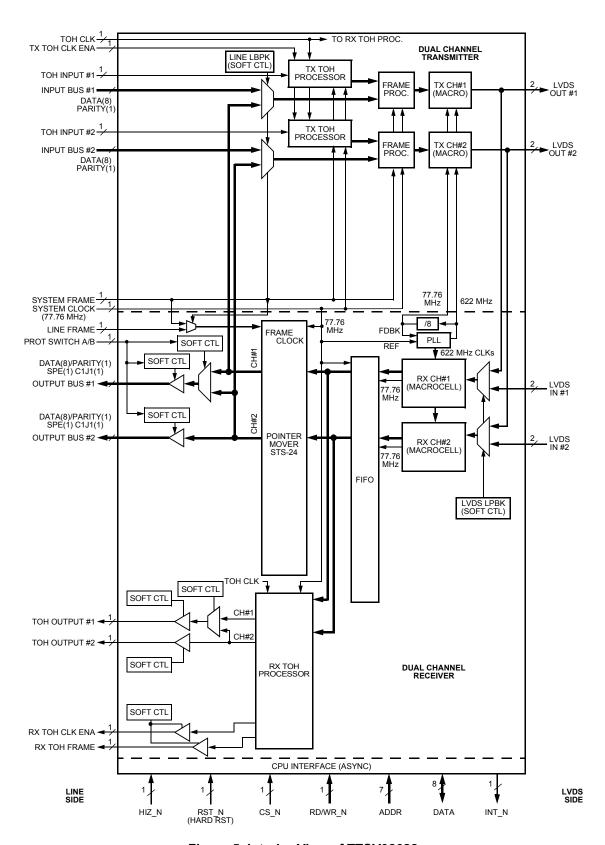

The TTSV02622 is composed of transmit (Tx) and receive (Rx) sections. The device (see Figure 1 on page 2) receives two byte-wide data streams at 77.76 MHz (STS-12 rate) and the associated clock. The incoming streams are framed, and descrambled before they are then written into a FIFO that absorbs phase and delay variations and allows the shift to system clock. The TOH is then extracted and sent out on the two serial ports. The pointer interpreter will then put the synchronous transport signal (STS) synchronous payload envelopes (SPEs) into a small elastic store from which the pointer generator will produce two byte-wide STS-12 streams of data that are aligned to the line timing pulse.

# **Architecture** (continued)

Figure 5. Interior View of TTSV02622

### **Architecture** (continued)

The alignment FIFO allows the transfer of all data to the system clock. The FIFO sync block allows the system to be configured to allow the frame alignment of multiple slightly varying data streams (see the FIFO Sync Subblock (Backplane to Line) section on page 28).

Figure 6. Interconnect of Streams for FIFO Alignment

The pointer mover (see the Pointer Mover Subblock (Backplane to Line) section on page 28) is responsible for mapping incoming frames to line frames. The pointer mover is a pseudo SONET implementation which is streamlined wherever possible to minimize gate count and complexity. As a result, it is only capable of correcting single bit, nonrepeating pointer errors. This pointer mover (i.e., interpreter, elastic store, and generator) will be capable of handling intra STS-12 concatenation as well as inter STS-12 concatenation as long as the STS-12 streams are frame aligned.

#### **Powerdown Mode**

Powerdown mode should be entered when the corresponding channel is disabled. Channels can be independently enabled or disabled under software control.

Note: The EXT PROT SW FUNC is low for STS-12 mode.

When a channel is disabled, the disabled channel of the clock and data recovery module is powered down, as well as the LVDS buffers and TTL buffers for that channel. When all channels are powered down, PLL in the CDR module is also powered down.

In addition, a pin has been added to enable the LVDS pins during boundary scan. This pin should be pulled high on the board for functional operation.

# **Supervisory Features**

- Parallel bus integrity:

- Parity error checking is implemented on each of the four parallel input buses. Even and odd parity is supported as controlled from the CPU interface (per device control). Upon detection of an error, an interrupt is raised. This feature is on a per-channel basis.

Note: On parallel output ports, parity is calculated over the 8-bit data bus and not on the SPE and C1J1 lines.

- TOH serial port integrity:

- There is even parity generation on each of the four TOH serial output ports. There is even parity error checking on each of the four TOH serial input ports. There is one parity bit imbedded in the TOH frame. It occupies the most significant bit location of A1 byte of STS-1. Upon detection of an error, an interrupt is raised. This feature is on a per-channel basis.

- LVDS link integrity:

- There is B1 parity generation on each of the four LVDS output channels. There is also performance monitoring on each of the four LVDS input channels, implemented as B1 parity error checking. Upon detection of an error, a counter is incremented (one count per errored bit) and an interrupt is raised. The counter is 7 bits wide plus one overflow indicator bit. This feature is on a per-channel basis.

- Framer monitor:

- The framer in the receive direction will report loss of frame (LOF) as an interrupt, as well as a LOF count and errored frame count. The LOF interrupt must not be clearable as long as the channel is in the LOF state. In addition, the errored frame count must represent errored frames, and should not increment more than once per frame even if there are multiple errors.

- Receiver internal path integrity:

- There is even parity generation in the receiver section (after descrambler). There is also even parity error checking in the receiver section (before output). Upon detection of an error, an interrupt is raised. This feature is on a per-channel basis.

- Pointer mover performance monitoring:

- There is pointer mover performance monitoring in the receiver section. Alarm indication signal path (AIS-P)

and concatenation is reported, as well as elastic store overflows.

- AIS-P is implemented as a per STS-1 interrupt. In case of concatenated payload, only the interrupt associated with the head of the group will be active.

- Concatenation is reported as a per STS-1 status, and is high when STS-1 is concatenated; and low when not concatenated.

- Elastic store overflow will generate an interrupt on a per STS-1 basis.

- FIFO aligner monitoring:

- There is monitoring of the FIFO aligner operating point, and upon deviating from the nominal operating point of the FIFO by more than user-programmable threshold values (min and max threshold values), an interrupt is raised. Threshold values are defined per device, flags are per channel.

- Frame offset monitoring:

- There is monitoring of the frame offset between all enabled channels (disabled channels must not interfere with the monitoring). Monitoring is performed continuously. Upon exceeding the maximum allowed frame offset (18 bytes) between all enabled channels, an interrupt is raised.

- CPU interface monitoring:

- There is monitoring of potential write cycles that may occur when operating in write protect mode. Upon detecting a write access to the application specific integrated circuit (ASIC) when the device is in write protect mode, an interrupt is raised (W-LOCK flag).

#### **Test Features**

#### ■ Line loopback:

— There is a line loopback feature allowing the user to perform a loopback on the line side (per device control). The line frame signal used by the pointer mover is automatically replaced by the system frame signal when operating in line loopback mode.

### ■ LVDS loopback:

— There is a LVDS loopback feature allowing the user to perform a loopback on the LVDS side (per device control).

#### ■ A1/A2 error insert:

— There is a frame error inject feature, in the transmitter section, allowing the user to replace framing bytes A1/A2 (only last A1 byte and first A2 byte) with a selectable A1/A2 byte value for a selectable number of consecutive frames. The number of consecutive frames to alter is specified by a 4-bit field, while A1/A2 value is specified by two 8-bit fields. The error insert feature is on a per-channel basis, A1/A2 values and 4-bit frame count value are on a per-device basis.

#### ■ B1 error insert:

— There is a B1 error insert feature, in the transmitter section, allowing the user to insert errors on user selectable bits in the B1 byte. Errors are created by simply inverting bit values. Bits to invert will be specified through an 8-bit register (each bit is associated with one of the eight B1 bits). To insert an error, software will first set the bits in the transmitter B1 error insert mask. Then, on a per-channel basis, software will write a one to the b1 error insert command. The insertion circuitry performs a rising edge detect on the bit, and will issue a corruption signal for the next frame, for one frame only. This feature is on a per-channel basis.

#### ■ TOH serial output port parity error insert:

— There is a parity error inject feature, in the receive section, allowing the user to invert the parity bit of each serial output port. This feature inserts a single error. This feature is on a per-channel basis.

#### ■ Parallel output bus parity error insert:

— There is a parity error inject feature, in the receive section, allowing the user to invert parity lines associated with each output parallel buses. This feature inserts a single error. This feature is on a per-channel basis. This feature supports both even and odd parities.

### Scrambler/descrambler disable:

— There is a scrambler/descrambler disable feature, allowing the user to disable the scrambler of the transmitter and the descrambler of the receiver. The B1 is calculated (in transmitter and receiver) on the nonscrambled data stream. This feature is per device.

# **Transmit Direction (Line to Backplane)**

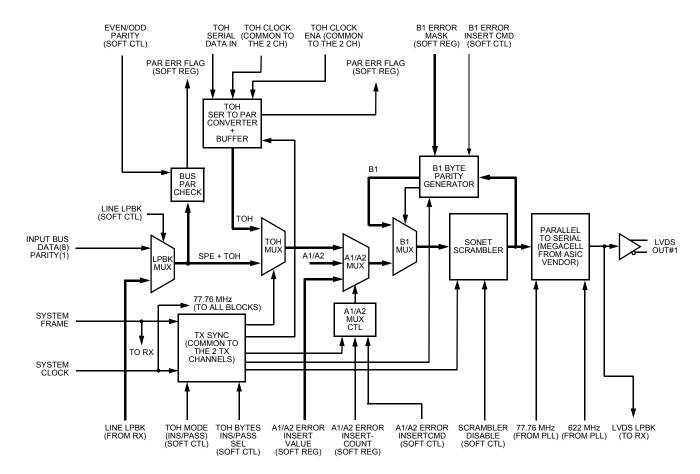

Each TOH insert block receives two byte-wide 77.76 MHz data from the line, which nominally represents two STS-12 streams (A and B). Transport overhead bytes are then optionally inserted into these streams and the streams are forwarded to the HSI. All byte timing pulses required to isolate individual overhead bytes (e.g., A1, A2, B1, D1—D12, etc.) are generated internally based on a Frame\_Sync received from the system (SYS\_FP).

- A1 and A2 insertion and optional corruption.

- H1, H2, and H3 pass through transparently.

- B1 calculation (after scrambling), insertion and optional corruption (before scrambling).

- Optional K1 and K2 insert.

- Optional S1/M0 insert.

- Optional E1/F1/E2 insert.

- Optional section and line data communication channel (DCC, D1—D12) insertion (for intercard communications channel).

- Scrambling of outgoing data stream with optional scrambler disabling.

- Optional stream disabling.

All streams operate byte wide at 77.76 MHz (622 Mbits/s) in all modes.

Figure 7. Transmitter Block

# Transmit Direction (Line to Backplane) (continued)

# **Transport Overhead Serial Link**

The TOH serial links are used to insert TOH bytes into the transmit data. TOH\_IN and TOH\_CLK\_EN get retimed by TOH\_CLK in order to meet setup and hold specifications of the device.

Insertion or passthrough of the TOH is under software control.

TOH parity is calculated using the initial retimed data (TOH IN D).

### A1/A2 Frame Insert and Corruption

When not corrupted, for each stream, all twelve A1 bytes of the STS-12 are set to 0xF6 and all twelve A2 bytes of the STS-12 are set to 0xE6 and all twelve A2 bytes of the STS-12 are set to 0xE6.

Corruption is controlled per stream by the A1/A2 error insert register. When A1/A2 corruption is set for a particular stream, the A1/A2 value in the corrupted A1/A2 value registers are sent for the number of frames defined in the corrupted A1/A2 frame count register (see Table 6 on page 33 and Table 7 on page 36 for register details).

**Note:** When the corrupted A1/A2 frame count register is set to zero, A1A2 corruption will continue until the A1/A2 error insert register is cleared, i.e., indefinitely.

On a per-device basis, the A1 and A2 byte values are set, as well as the number of frames of corruption. Then, to insert the specified A1/A2 values, each channel has an enable register. When the enable register is set, the A1/A2 values are corrupted for the number specified in the number of frames to corrupt. To insert errors again, the per-channel fault insert register must be cleared, and set again.

Only the last A1 and the first A2 are corrupted.

### **B1 Calculation and Insertion**

The B1 calculation block computes a BIP-8 code, using even parity over all bits of the previous STS-n frame after scrambling and is inserted in the B1 byte of the current STS-n frame before scrambling. Per-bit B1 corruption is controlled by the force BIP-8 corruption register (per device register). For any bit set in this register, the corresponding bit in the calculated BIP-8 is inverted before insertion into the B1 byte position. Each stream has an independent fault insert register that enables the inversion of the B1 bytes. B1 bytes in all other STS-1s in the stream are passed through transparently.

#### Stream Disable

When disabled via the appropriate bit in the stream enable register, the prescrambled data for a stream is set to all ones, feeding the HSI. The HSI macro is powered down on a per-stream basis, as is the LVDS outputs.

#### Scrambler

The data stream is scrambled using a frame synchronous scrambler of sequence length 127, operating at the line rate. The scrambling function can be disabled by software.

The generating polynomial for the scrambler is  $1 + x^6 + x^7$ .

The scrambler is reset to 111\_1111 on the first byte of the SPE (byte following the Z0 byte in the twelfth STS-1). That byte and all subsequent bytes to be scrambled are exclusive ORed, with the output from the byte-wise scrambler. The scrambler runs continuously from that byte on throughout the remainder of the frame.

A1, A2, J0, and Z0 bytes are not scrambled.

## **Receiver Block**

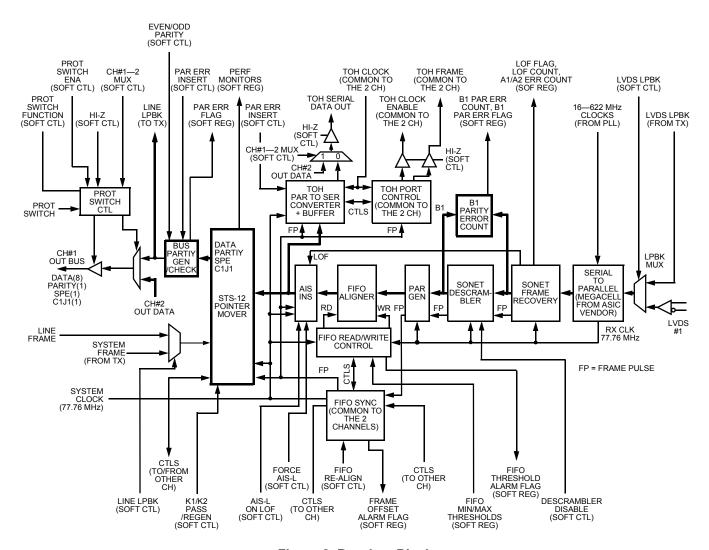

Figure 8. Receiver Block

#### Framer Subblock (Backplane to Line)

The framer block takes byte-wide data from the HSI, and outputs a byte-aligned byte-wide stream and 8 kHz sync pulse (asserted one clock before the first A1 byte). The framer algorithm determines the out-of-frame/in-frame status of the incoming data and will cause interrupts on both an errored frame and an OOF state.

### **Features**

- A1—A2 framing pattern detection.

- Framing similar to SONET specification.

- Generates timing and an 8 kHz frame pulse.

- Detects OOF and generates an interrupt.

- Detects errored frame and increments counter.

# Framer Subblock (Backplane to Line) (continued)

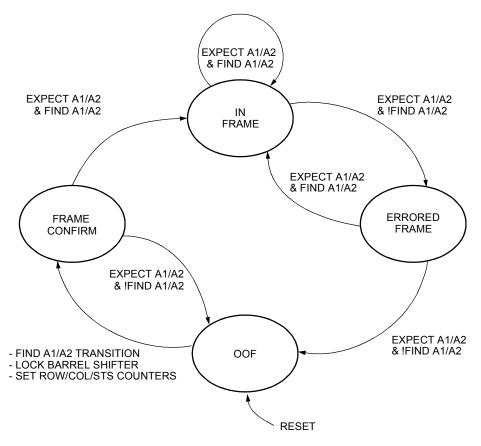

#### **Framer State Machine**

Figure 9 shows the state machine that controls the framer. Since the TTSV02622 is intended for use between ASICs via a backplane, there is only one errored frame state; thus, after two transitions are missed, the state machine goes into the OOF state and there is no SEF or LOF indication.

**OOF State.** In this state, the A1 pattern is searched for on every clock cycle.

A second stage of comparison is implemented to locate the A1/A2 transition. When the A1/A2 transition is found, the following occurs:

- The state machine moves from the OOF state to the frame confirm state.

- The A1offset for the byte start location is locked.

- The row, column, and STS counters are set.

**Frame Confirm.** In this state, the A1/A2 transition is only compared for at the appropriate location, i.e., beginning at the twelfth A1 location. This location is determined from the row, column, and STS counters which were set at the transition from OOF to frame confirm. If at this time the comparison fails, the state machine reverts to the OOF state. If the comparison passes, the next state will be In frame.

**In Frame.** This state is similar to the frame confirm state except that if the comparison at the A1/A2 time is incorrect, the next state will be the errored frame state. If the comparison is correct, the next state will be in frame.

**Errored Frame.** Once the errored frame state has been reached, if the next comparison is incorrect, the next state will be OOF. Otherwise, if correct, the next state will be in frame. This state will generate an error interrupt to the micro.

# Framer Subblock (Backplane to Line) (continued)

Notes:

Row, column, and STS counters are only set/reset by state transition from OOF to frame confirm.

Expect A1/A2 means that row/col/STS counter values indicate time for last (twelfth) A1 byte.

Figure 9. Framer State Machine

### B1 Calculate and Descramble (Backplane to Line)

Each Rx block receives byte-wide scrambled 77.76 MHz data and a frame sync from the framer. Since each HSI is independently clocked, the Rx block operates on individual streams. Timing signals required to locate overhead bytes to be extracted are generated internally based on the frame sync. The frame sync occurs one clock pulse before the first A1 byte of the stream. The Rx block produces byte-wide descrambled data and an output frame sync for the alignment FIFO block. The output frame sync occurs two clocks before the first A1 byte of the descrambled data stream to allow for metastable hardening by the write control subblock.

On the received data, the following functionality is needed:

- Descrambling of received data stream with optional descrambling disable.

- B1 verification.

#### Descrambling

The streams are scrambled using a frame synchronous scrambler of sequence length 127, operating at the line rate. The descrambling function can be disabled by software.

The generating polynomial for the scramble is  $1 + x^6 + x^7$ .

The scrambler is reset to 1111111 on the first byte of the SPE (byte following the Z0 byte in the twelfth STS-1). That byte and all subsequent bytes to be scrambled are exclusive ORed, with the output from the byte-wise scrambler. The scrambler runs continuously from that byte on throughout the remainder of the frame.

A1, A2, J0, and Z0 bytes are not scrambled.

#### **B1 Verification**

The B1 calculation block computes a BIP-8 code, using even parity over all bits of the previous STS-12 frame before descrambling, and this value is checked against the B1 byte of the current frame after descrambling. A perstream B1 error counter is incremented for each bit that is in error.

#### Alarm Indication Signal Line (AIS-L) Insertion

If enabled via AIS\_L\_INSERT[x] bit in the AIS\_L force register, AIS-L is inserted into the received frame by writing all ones for all bytes of the descrambled stream.

#### **AIS-L Insertion on Out of Frame**

If enabled via the appropriate bit in the AIS\_L force on out of frame register, AIS-L is inserted into the received frame by writing all ones for all bytes of the descrambled stream when the framer indicates that an out of frame condition exists.

## **Internal Parity Generation**

An even parity is generated on all data bytes and is routed in parallel with the data to be checked before the protection switch MUX at the parallel output.

## FIFO Subblock (Backplane to Line)

The FIFO subblock consists of a 24 by 10-bit FIFO per STS-12. This FIFO will be used to align up to ±154.3 ns of interlink skew and to transfer to the system clock.

#### FIFO Sync Subblock (Backplane to Line)

This FIFO sync block takes metastable hardened frame pulses from the write control blocks and produces sync signals that indicate when the read control blocks should begin reading from the first FIFO location. On top of the sync signals, this block produces an error indicator which indicates that the signals to be aligned are too far apart for alignment (i.e., greater than 18 clocks apart). Sync and error signals are sent to read control block for alignment.

The read control block is synchronized only once on start-up, and any further synchronizing is software (S/W) controlled. The action of resynchronizing a read control block will always cause a data hit. A software register allows the read control block to be resynchronized.

#### **Recommended Procedure for Synchronization of Selected Streams**

- Force AIS-L in all streams to be synchronized.

- Wait four frames.

- Write a 1 to the FIFO alignment resynchronizing register, bit DB1 of register 0x06.

- Wait four frames.

- Release the AIS-L in all streams.

#### Pointer Mover Subblock (Backplane to Line)

The pointer mover simply maps incoming frames to the line framing. The K1/K2 bytes and H1—SS bits are also passed through to the pointer generator so that the line can receive them. The mover will handle both concatenations inside the STS-12, and to other STS-12s inside the TTSV02622.

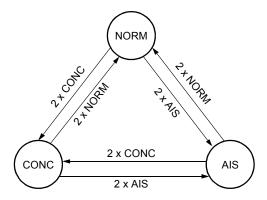

#### **Pointer Interpreter State Machine**

The pointer interpreter is minimized as much as possible to keep the gate count low. In keeping with that goal, the pointer interpreter has only three states (NORM, AIS, and CONC). The interpreter's highest priority is to maintain accurate dataflow (i.e., valid SPE only). This will ensure that any errors in the pointer value will be corrected by a standard pointer interpreter without any data hits. This means that error checking for increment, decrement, and NDF (i.e., 8 of 10) are maintained in order to ensure accurate dataflow. A single valid pointer (i.e., 0—782) that differs from the current pointer will be ignored. Two consecutive incoming valid pointers that differ from the current pointer will cause a reset of the J1 location to the latest pointer value (the generator will then produce an NDF). This block is designed to handle single bit errors without affecting dataflow or changing state, but it is not compliant with SONET standards.

# Pointer Mover Subblock (Backplane to Line) (continued)

Rules for Concatenation. The pointer mover block can correctly process any length of concatenation (multiple of three) as long as it begins on an STS-3 boundary (i.e., STS-1 number 1, 4, 7, 10, etc.) and is contained within the smaller of STS-3, 12 or 24 (see Table 4).

Table 4. Valid Starting Positions for a STS-MC

| STS-1<br>Number | STS-3c<br>SPE | STS-6c<br>SPE | STS-9c<br>SPE | STS-12c<br>SPE | STS-15c<br>SPE | STS-18c to STS-24c<br>SPEs |

|-----------------|---------------|---------------|---------------|----------------|----------------|----------------------------|

| 1               | Y             | Y             | Y             | Y              | Y              | Y                          |

| 4               | Y             | Y             | Y             | NO             | Y              | _                          |

| 7               | Y             | Y             | NO            | NO             | Y              | _                          |

| 10              | Y             | NO            | NO            | NO             | Y              | _                          |

| 13              | Y             | Y             | Υ             | Υ              | Y              | _                          |

| 16              | Y             | Y             | Y             | NO             | Y              | _                          |

| 19              | Y             | Y             | NO            | NO             | Y              | _                          |

| 22              | Y             | NO            | NO            | NO             | Y              | _                          |

#### Notes:

Y = STS-Mc SPE can start in that STS-1.

NO = STS-Mc SPE cannot start in that STS-1.

— = Y or NO, depending on the particular value of M.

#### Rules for Pointer Interpretation.

- NDF  $\leq$  N bits in H1 byte = (1001 + single bit error).

- NRMNBTS (i.e., NDF not set) ≤ N bits in H1 byte = (0110 + single bit error).

- CONC pointer ≤ (N bits in H1 byte = 1001 + single bit error) and offset = 11 1111 1111.

- AIS pointer ≤ offset and N bits are all 1s (SS bits are ignored).

- NORM pointer ≤ (offset 0—782) and (NDF or NRMNBITS).

### Pointer Mover Subblock (Backplane to Line) (continued)

**NORM State.** This state will begin whenever two consecutive NORM pointers are received. If two consecutive NORM pointers are received, such that both differ from the current offset, then the current offset will be reset to the last received NORM pointer. When the pointer interpreter changes its offset, it causes the pointer generator to receive a J1 value in a new position. When the pointer generator gets an unexpected J1, it resets its offset value to the new location and declares an NDF.

**Note:** The interpreter is only looking for two consecutive pointers that are different from the current value. These two consecutive NORM pointers **do not have to have the same value**.

For example; if the current pointer is 10 and you receive a NORM pointer with offset of 15 and a second NORM pointer with offset of 25, then the interpreter will change the current pointer to be 25.

**CONC State.** The receipt of two consecutive CONC pointers causes this state to be entered. Once in this state, offset values from the head of the concatenation chain are used to determine the location of the STS SPE for each STS in the chain.

**AIS State.** Two consecutive AIS pointers cause this state to occur. Any two consecutive normal or concatenation pointers will end this state. This state will cause the data leaving the pointer generator to be overwritten with 0xFF.

Figure 10. Pointer Mover State Machine

### **Pointer Generator**

The pointer generator simply maps the corresponding bytes into their appropriate location in the outgoing byte stream. The generator also creates offset pointers based on the location of the J1 byte as indicated by the pointer interpreter. The generator will signal NDFs when the interpreter signals that it is coming out of AIS state. The generator resets the pointer value and generates NDF every time a byte marked J1 is read from the elastic store that doesn't match the previous offset.

Increments and decrements signals from the pointer interpreter are latched once per frame on either the F1 or E2 byte times (depending on collisions), this ensures constant values during the H1 through H3 times. The choice of which byte time to do the latching on is made when the relative frame phases (i.e., received and system) is determined. This latch point will then be stable, unless the relative framing changes and the received H byte times collide with the system F1 or E2 times, in which case the latch point would be switched to the collision-free byte time.

### Pointer Mover Subblock (Backplane to Line) (continued)

There is no restriction on how many or how often increments and decrements are processed. Any received increment or decrement is immediately passed to the generator for implementation regardless of when the last pointer adjustment was made. The responsibility for meeting the SONET criteria for max frequency of pointer adjustments is then left to the upstream pointer processor.

When the interpreter signals an AIS state, the generator will immediately begin sending out 0xFF in place of data and H1, H2, H3. This will continue until the interpreter returns to NORM or CONC states and a J1 byte is received.

## **Miscellaneous Functions**

### K1/K2, A1/A2 Handling

K1/K2 bytes can be optionally passed through the pointer mover under software control, or it can be set to zero with the other TOH bytes. A1/A2 bytes are regenerated and set to F6 and 28, respectively.

# **SPE C1J1 Outputs**

In an attempt to minimize the complexity required from the pointer processor that may be hooked-up to the TTSV02622 parallel output port, two signals (per channel) must be provided to the external world; these are called SPE and C1J1. These two signals will allow a pointer processor to extract payload without interpreting the pointers.

Table 5. SPE and C1J1 Functionality

| SPE | C1J1 | Description                                   |

|-----|------|-----------------------------------------------|

| 0   | 0    | TOH information excluding C1(J0) of STS-1 #1. |

| 0   | 1    | Position of C1(J0) of STS-1 #1.               |

| 1   | 0    | SPE information excluding the 12 J1 bytes.    |

| 1   | 1    | Position of the twelve J1 bytes.              |

The following rules must be observed for generating SPE and C1J1 signals:

- On occurrence of AIS-P on any of the STS-1, there must be no corresponding J1 pulse.

- In case of concatenated payloads (up to STS-24c), only the head STS-1 of the group must have an associated J1 pulse.

- C1J1 signal must track any pointer movements.

- During a negative justification event, SPE must be set high during the H3 byte to indicate that payload data is available.

- During a positive justification event, SPE must be set low during the positive stuff opportunity byte to indicate that payload data is not available.

# Registers

# **Definition of Register Types**

The TTSV02622 design contains six structural register elements: SREG, CREG, PREG, IAREG, ISREG, and IEREG. There are no mixed registers in TTSV02622. This means that all bits of a particular register (particular address) are structurally the same and are as follows:

- Status register (SREG):

- A status register is read only, and as the name implies is used to convey the status information of a particular element or function of the TTSV02622 chip. The reset value of an SREG is really the reset value of the particular element or function that is being read. In some cases, an SREG is really a fixed value; an example of which is the fixed id and revision registers.

- Control register (CREG):

- A control register is read and writable memory element inside CORE\_CONTROL. The value of a CREG will always be the value written to it. Events inside the TTSV02622 chip cannot affect a CREG value. The only exception is a soft reset, in which case the CREG will return to its reset value. The control register have reset values as defined in the reset value column of Table 6 on page 33.

- Pulse register (PREG):

- Each element, or bit, of a pulse register is a control or event signal that is asserted and then deasserted when a value of 1 is written to it. This means that each bit is always of value 0 until it is written to, upon which it is pulsed to the value of 1 and then returned to a value of 0. A pulse register will always have a read value of 0.

- Interrupt alarm register (IAREG):

- Each bit of an interrupt alarm register is a event latch. When a particular event is produced in the TTSV02622 chip, its occurrence is latched by its associated IAREG bit. To clear a particular IAREG bit, a value of 1 must be written to it. In the TTSV02622 chip, all IAREG reset values are 0.

- Interrupt status register (ISREG):

- Each bit of an interrupt status register is physically the logical OR function. It is a consolidation of lower-level interrupt alarms and/or ISREG bits from **other** registers. A direct result of the fact that each bit of the ISREG is a logical OR function means that it will have a read value of 1 if any of the consolidation signals are of value 1, and will be of value 0 if and only if all consolidation signals are of value 0. In the TTSV02622 chip, all ISREG reset values are 0.

- Interrupt enable register (IEREG):

- Each bit of a status register or alarm register has an associated enable bit. If this bit is set to value 1, then the event is allowed to propagate to the next higher level of consolidation. If this bit is set to zero, then the associated IAREG or ISREG bit can still be asserted but an alarm will not propagate to the next higher level. Obviously, an interrupt enable bit is an interrupt mask bit when it is set to value 0.

# Registers (continued)

# **Register Map**

## Table 6. Register Map

| ADDR*<br>[6:0] | Reg.<br>Type | DB7                              | DB6                                   | DB5                                         | DB4                                                                    | DB3                                             | DB2                                                    | DB1                                          | DB0                                                  | Reset<br>Value<br>(hex) | Comments                          |  |  |  |

|----------------|--------------|----------------------------------|---------------------------------------|---------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------|----------------------------------------------|------------------------------------------------------|-------------------------|-----------------------------------|--|--|--|

| 00             | SREG         |                                  | FIXED ID MSB                          |                                             |                                                                        |                                                 |                                                        |                                              |                                                      |                         |                                   |  |  |  |

| 01             | SREG         |                                  | 01                                    | register<br>block.                          |                                                                        |                                                 |                                                        |                                              |                                                      |                         |                                   |  |  |  |

| 02             | SREG         |                                  | FIXED REV                             |                                             |                                                                        |                                                 |                                                        |                                              |                                                      |                         |                                   |  |  |  |

| 03             | CREG         |                                  |                                       |                                             | SCRAT                                                                  | CH PAD                                          |                                                        |                                              |                                                      | 00                      |                                   |  |  |  |

| 04             | CREG         |                                  |                                       |                                             | LOCKR                                                                  | EG MSB                                          |                                                        |                                              |                                                      | 00                      |                                   |  |  |  |

| 05             | CREG         |                                  |                                       |                                             | LOCKF                                                                  | REG LSB                                         |                                                        |                                              |                                                      | 00                      |                                   |  |  |  |

| 06             | PREG         | _†                               | <u>_</u> †                            | <u>_</u> †                                  | <u>_</u> †                                                             | <u>_</u> †                                      | t                                                      | FIFO<br>ALIGNMENT<br>COMMAND                 | GLOBAL<br>RESET<br>COMMAND                           | NA                      |                                   |  |  |  |

|                |              |                                  |                                       |                                             | Device R                                                               | egister Block                                   |                                                        |                                              |                                                      |                         |                                   |  |  |  |

| 08             | CREG         | _+                               | _†                                    | <u>_</u> †                                  | Rx TOH<br>FRAME<br>AND<br>Rx TOH<br>CLOCK<br>ENABLE<br>HI-Z<br>CONTROL | EXT PROT<br>SW EN                               | EXT PROT<br>SW FUNC                                    | STS-12<br>SELECT                             | LVDS LPBK<br>CONTROL                                 | 00                      | Device<br>register block<br>(Rx). |  |  |  |

| 09             | CREG         |                                  | _†                                    | <u>_</u> †                                  | _†                                                                     | <u>_</u> †                                      | PARALLEL<br>PORT<br>OUTPUT<br>MUX<br>SELECT<br>FOR CH1 | _†                                           | SERIAL<br>PORT<br>OUTPUT<br>MUX<br>SELECT<br>FOR CH1 | 0F                      |                                   |  |  |  |

| 0A             | CREG         | _†                               | _†                                    | _†                                          |                                                                        | FIFO ALIGNE                                     | R THRESHOLI                                            | D VALUE (min)                                |                                                      | 02                      |                                   |  |  |  |

| 0B             | CREG         | _†                               | †                                     | _†                                          |                                                                        | FIFO ALIGNER                                    | R THRESHOLD                                            | VALUE (max)                                  |                                                      | 15                      |                                   |  |  |  |

| 0C             | CREG         | †                                | SCRAMBLER/<br>DESCREAMBLER<br>CONTROL | I/O<br>PARALLEL<br>BUS<br>PARITY<br>CONTROL | LINE LPBK<br>CONTROL                                                   | LINE LPBK NUMBER OF CONSECUTIVE A1/A2 ERRORS TO |                                                        |                                              |                                                      |                         | Device<br>register block<br>(Tx). |  |  |  |